## ON THE LEVEL

We are now at a stage in the Logic course where we can design quite complex computer circuits. In this instalment, we will follow through the whole design process from initial specification, through truth table and simplified Boolean expression, to finished circuit diagram — for a parity bit generating circuit and a priority encoder.

Before beginning to look at the design of these two advanced applications, we will first take a detailed look at another important logic gate — the Exclusive OR (XOR) gate. This gate has already been briefly considered (see page 47), but we have not yet given the Boolean algebra or circuit diagram symbols for it:

| 3 | ruth Tabl | 8 | Circuit Symbol     |  |

|---|-----------|---|--------------------|--|

| A | B         | C |                    |  |

| 0 | 0         | 0 | XOR -C             |  |

| 0 | 1         | 1 | B-                 |  |

| 1 | 0         | 1 | Reduce Carled      |  |

| 1 | ିଶ୍ୱ      | 0 | Boolean Symbol = 🕀 |  |

From the truth table, it can be seen that the output C can be expressed in two ways:

a)  $C = A \oplus B = \overline{A} \cdot B + A \cdot \overline{B}$ b)  $\overline{C} = \overline{A \oplus B} = \overline{A} \cdot \overline{B} + A \cdot \overline{B}$

The second expression is formed by considering the cases when C is not one (i.e. zero). This gate will be of particular use in our first application.

| A | 8  | C   | D  | P. |

|---|----|-----|----|----|

| 0 | 0  | 0   | 0  | 0  |

| 0 | 0  | 0   | 1  | -1 |

| 0 | 0  | 1   | 0  | 1  |

| 0 | 0  | 0 1 |    | 0  |

| 0 | 1  | 0   | 0  | 1  |

| 0 | 1  | 0   | 1  | 0  |

| 0 | 1  | 1   | 0  | 0  |

| 0 | 1  | 1   | 1  | 1  |

| Ť | 0  | 0   | 0  | 1  |

| 1 | 0  | 0   | 1  | 0  |

| 1 | 0  | 1   | 0  | 0  |

| 1 | 0  | 1   | 1) | 1  |

| ŧ | 1  | 0   | 0  | 0  |

| 1 | 1. | 0   | 1  | 1  |

| 1 | ŧ  | 1   | 0  | Ŧ  |

| t | Ť  | 1   | 1  | 0  |

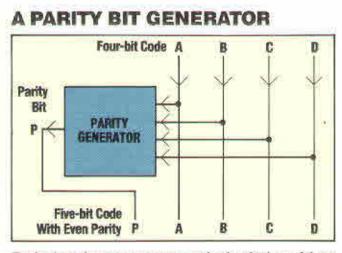

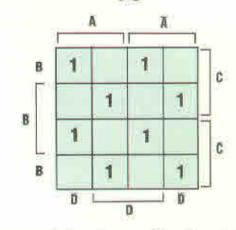

Parity is an important concept in the design of data transmission systems. The parity bit (see previous diagram) of a binary code is added to the rest of the code in order to make all the codes transmitted have an even number of ones. (Another convention is to make all the codes contain an odd number of ones — this is known as *odd parity*). A parity bit acts as a checking system to ensure that the correct transmission has taken place. The circuit we shall design will accept a four-bit code and produce an appropriate parity bit. With a small modification the circuit may also act as a parity checker of incoming data. The truth table for this circuit is given in the margin. Representing these values on a k-map gives:

The symmetrical pattern produced on the k-map, unfortunately, does not allow simplification because no groups can be formed. The resulting expression for P is:

## $P=\overline{A}.\overline{B}.\overline{C}.D+\overline{A}.\overline{B}.C.\overline{D}+\overline{A}.B.\overline{C}.\overline{D}+\overline{A}.B.C.D$ $+A.\overline{B}.\overline{C}.\overline{D}+A.\overline{B}.C.D+A.\overline{B}.\overline{C}.D+A.\overline{B}.C.\overline{D}$

By grouping the red terms together and the blue terms together, we can simplify the expression:

$P = (\overline{A}.\overline{B} + A.B).(\overline{C}.D + C.\overline{D}) + (A.\overline{B} + \overline{A}.B).(\overline{C}.\overline{D} + C.D)$

Now, by referring to the expressions for an XOR gate that we introduced at the start of this article, we can further simplify the expression to get:

$P=(\overline{A\oplus B}).(C\oplus D)+(A\oplus B).(\overline{C\oplus D})$

By considering each bracketed term as an input to an XOR gate, the expression may be further reduced:

$$P = (A \oplus B) \oplus (C \oplus D)$$

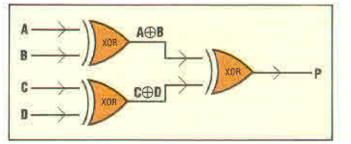

and the circuit formed is a 'cascade' of XOR gates: